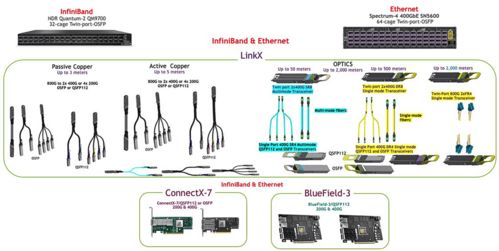

基于100G PAM4技術(shù)的LinkX線纜及其在計(jì)算機(jī)軟硬件研發(fā)中的關(guān)鍵角色

隨著數(shù)據(jù)中心、高性能計(jì)算和人工智能應(yīng)用對(duì)數(shù)據(jù)傳輸速率要求的爆炸式增長(zhǎng),傳統(tǒng)非歸零碼(NRZ)技術(shù)在高帶寬需求面前已顯乏力。在這一背景下,基于四級(jí)脈沖幅度調(diào)制(PAM4)技術(shù)的100G LinkX線纜應(yīng)運(yùn)而生,成為下一代高速互連的關(guān)鍵物理層解決方案,并深刻影響著計(jì)算機(jī)軟硬件的研發(fā)方向。

一、PAM4技術(shù)與100G LinkX線纜的技術(shù)核心

PAM4技術(shù)是一種先進(jìn)的信號(hào)調(diào)制方式,它允許每個(gè)符號(hào)周期傳輸2比特信息(四種電平),相較于NRZ技術(shù)每個(gè)符號(hào)僅傳輸1比特信息,在相同帶寬下有效將數(shù)據(jù)速率提升了一倍。100G LinkX線纜正是利用這一原理,在有限的物理通道(如銅纜或光纖)上實(shí)現(xiàn)100Gbps甚至更高的傳輸速率。這類線纜通常指有源電纜(AEC),集成了信號(hào)調(diào)理芯片(如重定時(shí)器Retimer或重驅(qū)動(dòng)器Redriver),能夠有效補(bǔ)償信號(hào)在傳輸過程中的衰減和失真,從而支持更長(zhǎng)的傳輸距離和更高的信號(hào)完整性。

二、對(duì)硬件研發(fā)的驅(qū)動(dòng)與挑戰(zhàn)

- 高速接口芯片設(shè)計(jì):硬件研發(fā)的核心在于支持PAM4信號(hào)的專用集成電路(ASIC)和物理層(PHY)芯片。這要求芯片設(shè)計(jì)必須處理更復(fù)雜的信號(hào)調(diào)制、更嚴(yán)格的時(shí)序容限以及更高的功耗管理挑戰(zhàn)。SerDes(串行器/解串器)設(shè)計(jì)需升級(jí)以支持PAM4信令,包括高性能模數(shù)/數(shù)模轉(zhuǎn)換器、自適應(yīng)均衡器和前向糾錯(cuò)(FEC)模塊。

- PCB與連接器設(shè)計(jì):主板、網(wǎng)卡、交換機(jī)的印刷電路板(PCB)設(shè)計(jì)必須應(yīng)對(duì)更高速率帶來的信號(hào)完整性挑戰(zhàn)。需要采用更先進(jìn)的材料(如低損耗介質(zhì))、更精密的布線規(guī)則(如阻抗控制、串?dāng)_抑制)以及支持更高頻率的連接器(如QSFP-DD, OSFP)。

- 系統(tǒng)集成與測(cè)試:將支持100G PAM4的LinkX線纜集成到服務(wù)器、交換機(jī)、存儲(chǔ)陣列中,需要全新的系統(tǒng)級(jí)驗(yàn)證和測(cè)試方法。研發(fā)重點(diǎn)包括通道仿真、眼圖測(cè)試、誤碼率(BER)測(cè)試以及熱插拔和互操作性測(cè)試,確保在真實(shí)環(huán)境中的穩(wěn)定可靠。

三、對(duì)軟件研發(fā)的影響與協(xié)同

- 驅(qū)動(dòng)與固件開發(fā):硬件功能的發(fā)揮離不開底層軟件的支持。需要開發(fā)或升級(jí)網(wǎng)絡(luò)接口卡(NIC)、交換芯片的驅(qū)動(dòng)程序、固件(Firmware)和底層管理軟件,以實(shí)現(xiàn)對(duì)PAM4鏈路的管理、狀態(tài)監(jiān)控(如信號(hào)質(zhì)量、溫度)、錯(cuò)誤診斷和動(dòng)態(tài)配置(如速率協(xié)商、功耗調(diào)整)。

- 網(wǎng)絡(luò)協(xié)議棧優(yōu)化:在應(yīng)用層,更高的物理帶寬要求網(wǎng)絡(luò)協(xié)議棧(如TCP/IP)能夠高效利用鏈路,避免成為瓶頸。軟件研發(fā)需關(guān)注零拷貝技術(shù)、內(nèi)核旁路(如DPDK、RDMA)、擁塞控制算法優(yōu)化等,以降低延遲、提升吞吐量,充分發(fā)揮100G鏈路的潛力。

- 管理與編排軟件:在大規(guī)模數(shù)據(jù)中心,成千上萬條100G鏈路需要集中管理。軟件研發(fā)需增強(qiáng)網(wǎng)絡(luò)管理平臺(tái)、遙測(cè)系統(tǒng)和自動(dòng)化編排工具(如基于SONiC的網(wǎng)絡(luò)操作系統(tǒng)),實(shí)現(xiàn)對(duì)高速鏈路的智能配置、性能監(jiān)控、故障預(yù)測(cè)和自動(dòng)化修復(fù)。

四、未來趨勢(shì)與研發(fā)展望

基于100G PAM4的LinkX線纜技術(shù)正向200G、400G乃至800G演進(jìn)。未來的研發(fā)將更加聚焦于:

- 共封裝光學(xué)(CPO):將光引擎與交換芯片更緊密集成,進(jìn)一步降低功耗和延遲。

- 硅光子學(xué)集成:利用硅工藝制造光學(xué)元件,實(shí)現(xiàn)光電集成芯片,降低成本與體積。

- 智能無損網(wǎng)絡(luò):通過軟硬件協(xié)同,在RoCEv2等協(xié)議下構(gòu)建完全無損的數(shù)據(jù)中心網(wǎng)絡(luò),滿足AI/HP計(jì)算需求。

- 安全性增強(qiáng):在物理層和數(shù)據(jù)鏈路層集成新的安全特性,防止竊聽和篡改。

100G PAM4 LinkX線纜不僅是高速連接的“血管”,更是驅(qū)動(dòng)計(jì)算機(jī)軟硬件協(xié)同創(chuàng)新、向下一代數(shù)據(jù)中心架構(gòu)演進(jìn)的催化劑。其研發(fā)是一個(gè)涵蓋材料科學(xué)、芯片設(shè)計(jì)、信號(hào)處理、系統(tǒng)集成和軟件優(yōu)化的跨學(xué)科系統(tǒng)工程,將持續(xù)引領(lǐng)計(jì)算與通信基礎(chǔ)設(shè)施的深刻變革。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.qhdadi.com.cn/product/67.html

更新時(shí)間:2026-04-28 17:08:25